- 您现在的位置:买卖IC网 > Sheet目录985 > ISLA224IR72EV1Z (Intersil)BOARD EVALUATION FOR ISLA224P

�� �

�

�

�ISLA224P�

�Typical� Performance� Curves�

�All� Typical� Performance� Characteristics� apply� under� the� following� conditions� unless� otherwise� noted:� AVDD� =� OVDD� =� 1.8V,� T� A� =� +25°C,�

�A� IN� =� -dBFS,� f� IN� =� 105MHz,� f� SAMPLE� =� 250MSPS.� (Continued)�

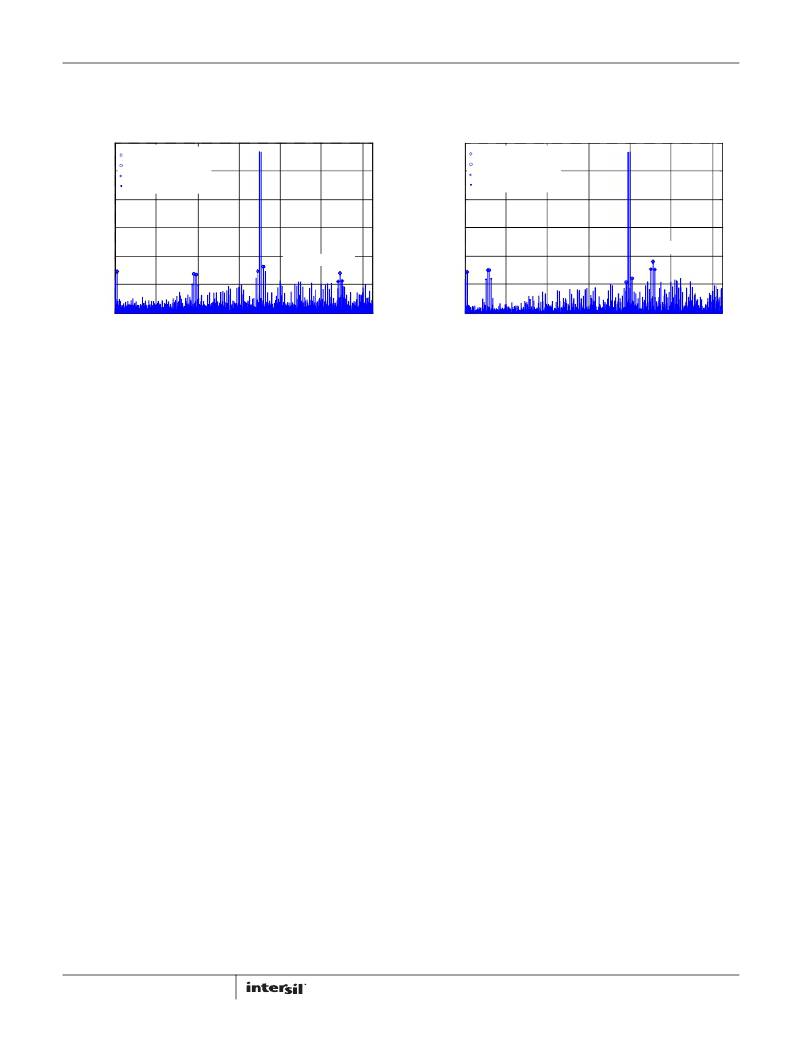

�0�

�IMD2�

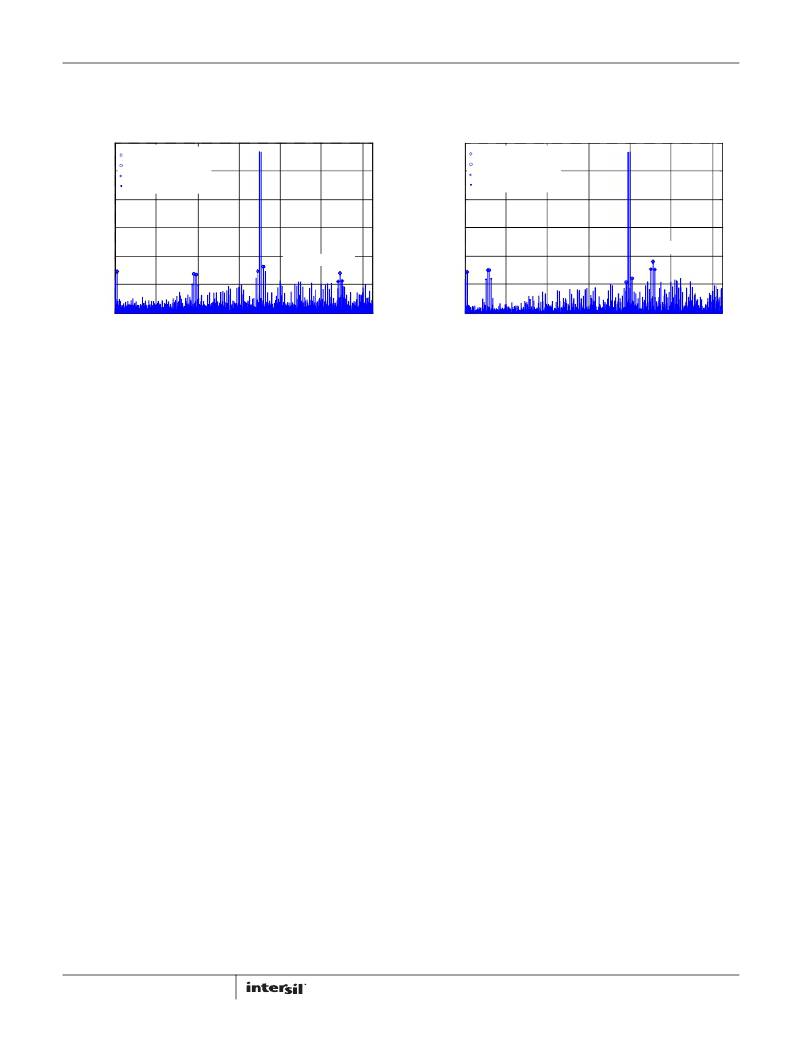

�0�

�IMD2�

�-20�

�IMD3�

�2ND� HARMONICS�

�-20�

�IMD3�

�2ND� HARMONICS�

�-40�

�-60�

�3RD� HARMONICS�

�-40�

�-60�

�3RD� HARMONICS�

�-80�

�-100�

�IMD3� =� 87dBFS�

�-80�

�-100�

�IMD3� =� 96dBFS�

�-120�

�0�

�20�

�40�

�60�

�80�

�100�

�120�

�-120�

�0�

�20�

�40�

�60�

�80�

�100�

�120�

�FREQUENCY� (MHz)�

�FIGURE� 19.� TWO-TONE� SPECTRUM�

�(F1� =� 70MHz,� F2� =� 71MHz� AT� -7dBFS)�

�Theory� of� Operation�

�Functional� Description�

�The� ISLA224P25� is� based� upon� a� 14-bit,� 250MSPS� A/D� converter�

�core� that� utilizes� a� pipelined� successive� approximation�

�architecture� (see� Figure� 21).� The� input� voltage� is� captured� by� a�

�Sample-Hold� Amplifier� (SHA)� and� converted� to� a� unit� of� charge.�

�Proprietary� charge-domain� techniques� are� used� to� successively�

�compare� the� input� to� a� series� of� reference� charges.� Decisions�

�made� during� the� successive� approximation� operations� determine�

�the� digital� code� for� each� input� value.� Digital� error� correction� is� also�

�applied,� resulting� in� a� total� latency� of� 10� clock� cycles.� This� is�

�evident� to� the� user� as� a� latency� between� the� start� of� a� conversion�

�and� the� data� being� available� on� the� digital� outputs.�

�Power-On� Calibration�

�As� mentioned� previously,� the� cores� perform� a� self-calibration� at�

�start-up.� An� internal� power-on-reset� (POR)� circuit� detects� the�

�supply� voltage� ramps� and� initiates� the� calibration� when� the�

�analog� and� digital� supply� voltages� are� above� a� threshold.� The�

�following� conditions� must� be� adhered� to� for� the� power-on�

�calibration� to� execute� successfully:�

�?� A� frequency-stable� conversion� clock� must� be� applied� to� the�

�CLKP/CLKN� pins�

�?� DNC� pins� must� not� be� connected�

�?� SDO� has� an� internal� pull-up� and� should� not� be� driven� externally�

�?� RESETN� is� pulled� low� by� the� ADC� internally� during� POR.�

�External� driving� of� RESETN� is� optional.�

�?� SPI� communications� must� not� be� attempted�

�16�

�FREQUENCY� (MHz)�

�FIGURE� 20.� TWO-TONE� SPECTRUM�

�(F1� =� 170MHz,� F2� =� 171MHz� AT� -7dBFS)�

�A� user-initiated� reset� can� subsequently� be� invoked� in� the� event�

�that� the� above� conditions� cannot� be� met� at� power-up.�

�After� the� power� supply� has� stabilized� the� internal� POR� releases�

�RESETN� and� an� internal� pull-up� pulls� it� high,� which� starts� the�

�calibration� sequence.� If� a� subsequent� user-initiated� reset� is�

�desired,� the� RESETN� pin� should� be� connected� to� an� open-drain�

�driver� with� an� off-state/high� impedance� state� leakage� of� less�

�than� 0.5mA� to� assure� exit� from� the� reset� state� so� calibration� can�

�start.�

�The� calibration� sequence� is� initiated� on� the� rising� edge� of�

�RESETN,� as� shown� in� Figure� 22.� Calibration� status� can� be�

�determined� by� reading� the� cal_status� bit� (LSB)� at� 0xB6.� This� bit� is�

�‘0’� during� calibration� and� goes� to� a� logic� ‘1’� when� calibration� is�

�complete.� The� data� outputs� produce� 0xCCCC� during� calibration;�

�this� can� also� be� used� to� determine� calibration� status.�

�If� the� selectable� clock� divider� is� set� to� 1� (default),� the� output�

�clock� (CLKOUTP/CLKOUTN)� will� not� be� affected� by� the� assertion�

�of� RESETN.� If� the� selectable� clock� divider� is� set� to� 2� or� 4,� the�

�output� clock� is� set� low� while� RESETN� is� asserted� (low).� Normal�

�operation� of� the� output� clock� resumes� at� the� next� input� clock�

�edge� (CLKP/CLKN)� after� RESETN� is� de-asserted.� At� 250MSPS� the�

�nominal� calibration� time� is� 200ms,� while� the� maximum�

�calibration� time� is� 550ms.�

�FN7570.1�

�November� 30,� 2012�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ISPTPKIT

SCREW KIT TAMPER RESISTANT 9PCS

ITCSN-0400-25-U

HEATSHRINK ITCSN 2/5" X 25'

JC2AF-TM-DC24V-F

RELAY GEN PURPOSE DPST 10A 24V

JJM1A-12V

RELAY AUTOMOTIVE SPST 20A 12V

JM1AN-ZTM-DC5V-F

RELAY GEN PURPOSE SPST 20A 5V

JQ1P-18V-F

RELAY GEN PURPOSE SPDT 10A 18V

JS1-F-6V-F

RELAY GEN PURPOSE SPDT 10A 6V

JSM1-9V-5

RELAY AUTOMOTIVE SPDT 15A 9V

相关代理商/技术参数

ISLA224P

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC

ISLA224P12

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:High Performance Dual 14-Bit, 125MSPS ADC

ISLA224P12IRZ

制造商:Intersil Corporation 功能描述:DUAL 14-BIT 125MSPS UNBUFFERED INPUT, 72-PIN - Trays 制造商:Intersil Corporation 功能描述:IC ADC 14BIT SPI/SRL 125M 48QFN 制造商:Intersil 功能描述:Dual 14-Bit 125MSPS Unbuffered Input, 72

ISLA224P13

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC

ISLA224P13IRZ

制造商:Intersil Corporation 功能描述:DUAL 14-BIT 130MSPS UNBUFFERED INPUT, 72-PIN - Trays 制造商:Intersil Corporation 功能描述:IC ADC 14BIT SRL/SPI 72QFN 制造商:Intersil 功能描述:DL 14-BIT 130MSPS UNBUFRED INPUT 72PIN

ISLA224P20

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC

ISLA224P20IRZ

制造商:Intersil Corporation 功能描述:DUAL 14-BIT 200MSPS UNBUFFERED INPUT, 72-PIN - Trays 制造商:Intersil Corporation 功能描述:IC ADC 14BIT SRL/SPI 72QFN 制造商:Intersil 功能描述:DL 14-BIT 200MSPS UNBUFRED INPUT 72PIN 制造商:Intersil Corporation 功能描述:IC, ADC, 14BIT; Resolution (Bits):14bit; Sampling Rate:200MSPS; Supply Voltage Type:Single; Supply Voltage Min:1.7V; Supply Voltage Max:1.9V; Supply Current:375mA; Digital IC Case Style:QFN; No. of Pins:72; Data Interface:SPI ;RoHS Compliant: Yes

ISLA224P25

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual 14-Bit, 250MSPS/200MSPS/130MSPS ADC